小型化晶振在電子設(shè)備中的應(yīng)用和影響

隨著電子設(shè)備不斷向小型化發(fā)展,晶振作為時(shí)鐘信號(hào)源的重要組成部分,也面臨著小型化和低功耗的趨勢(shì),。本文將探討小型化對(duì)晶振的起振時(shí)間、相位噪聲和抖動(dòng)的具體影響,,并分析如何選擇合適的晶振。

一,、小型化對(duì)晶振起振時(shí)間的影響

起振時(shí)間是晶振開(kāi)始工作并達(dá)到穩(wěn)定振蕩狀態(tài)所需的時(shí)間,,主要由晶體的諧振電阻和負(fù)性阻抗決定,。晶體的諧振電阻越小,,起振越快。高品質(zhì)的石英材料和精密切割技術(shù)可以減少晶體內(nèi)部缺陷,,提高品質(zhì)因數(shù)Q值,,從而減少起振時(shí)間。負(fù)性阻抗的大小由振蕩IC和負(fù)載電容CL決定,。在設(shè)計(jì)中合理選擇負(fù)載電容和優(yōu)化振蕩IC,,有助于在小型化條件下實(shí)現(xiàn)快速起振。

二,、小型化對(duì)晶振相位噪聲的影響

相位噪聲是振蕩信號(hào)頻域內(nèi)的不穩(wěn)定,,直接影響信號(hào)的純凈度和質(zhì)量。高Q值晶體能夠更好地濾除噪聲信號(hào),,降低相位噪聲,。高Q值的小型化晶振可以實(shí)現(xiàn)低相位噪聲的需求。合理選擇負(fù)載電容并優(yōu)化電路設(shè)計(jì),,平衡近端和遠(yuǎn)端相位噪聲,,是提高整體性能的關(guān)鍵。驅(qū)動(dòng)電路設(shè)計(jì)可以減少電源噪聲和電磁干擾對(duì)相位噪聲的影響,。采用低噪聲放大器和穩(wěn)壓電源,,可以進(jìn)一步降低相位噪聲,。

三、小型化對(duì)晶振抖動(dòng)的影響

抖動(dòng)是信號(hào)在時(shí)域內(nèi)的不穩(wěn)定,,主要有電源質(zhì)量和環(huán)境干擾引起的,。低噪聲的電源設(shè)計(jì)和濾波電路可以減少電源噪聲對(duì)抖動(dòng)的影響。穩(wěn)定干凈的電源是降低抖動(dòng)的基礎(chǔ),。電磁干擾和射頻干擾是引起抖動(dòng)的重要因素,。小型化晶振需要在設(shè)計(jì)中考慮屏蔽和隔離技術(shù),以減少外部干擾的影響,。

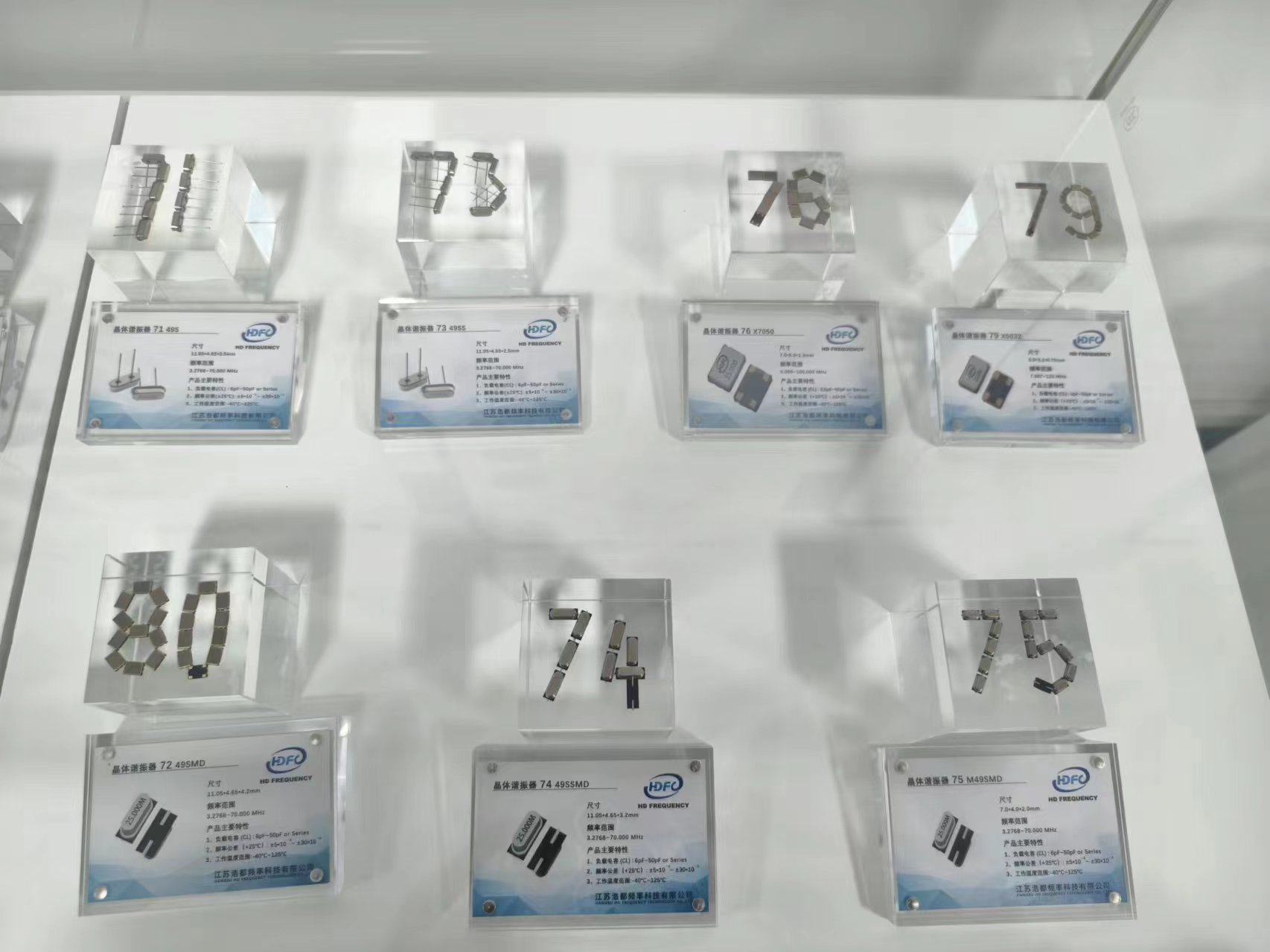

四,、如何選擇合適的晶振

在選擇晶振時(shí),需要考慮電子設(shè)備的需求,。如果設(shè)備需要較大的負(fù)載和較強(qiáng)的驅(qū)動(dòng)能力,,盡量選擇體積較大的晶體。在既要小體積又要驅(qū)動(dòng)能力較強(qiáng)的情況下,,可以選用驅(qū)動(dòng)能力較高的振蕩IC,。

文章來(lái)源:https://zhuanlan.zhihu.com/p/6428029948?